#### RTP n° 21 Paris, le 5 Novembre 2003 Evolution de la conception des « systemes sur une puce » a l,ere des nanotechnologies

Jean-Pierre SCHOELLKOPF Central R&D, Crolles, France

**STMicroelectronics**

### Agenda

Technology Evolution

- New system requirements

- Hardware/Software co-design

- Design Complexity and manufacturing costs

- Concurrent hard/software design and validation

- Flexible and Reconfigurable SoC

Conclusion

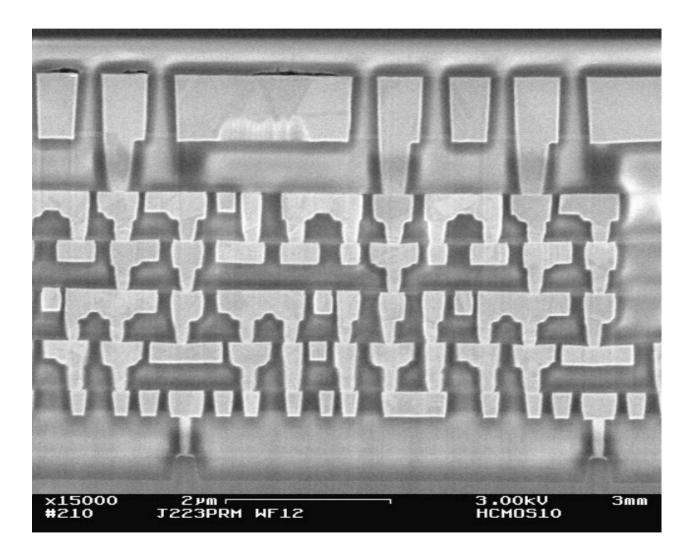

#### 90nm full SiOC/Cu interconnect

#### 65nm Process Development – Crolles2

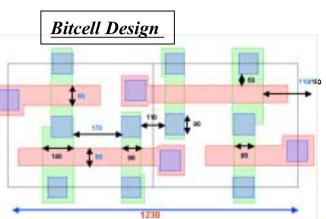

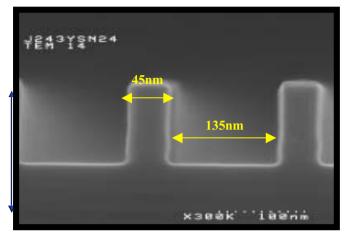

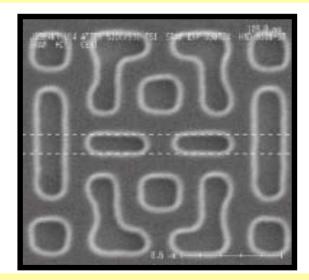

#### 0.69um2 Bitcell

Contact polish – (200nm Pitch)

RED 11-03

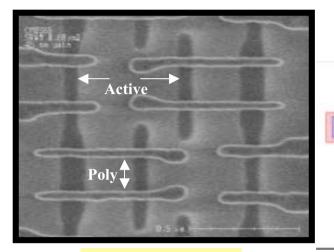

#### 45nm Gate – (180nm Pitch)

Line1 patterning – (200nm Pitch)

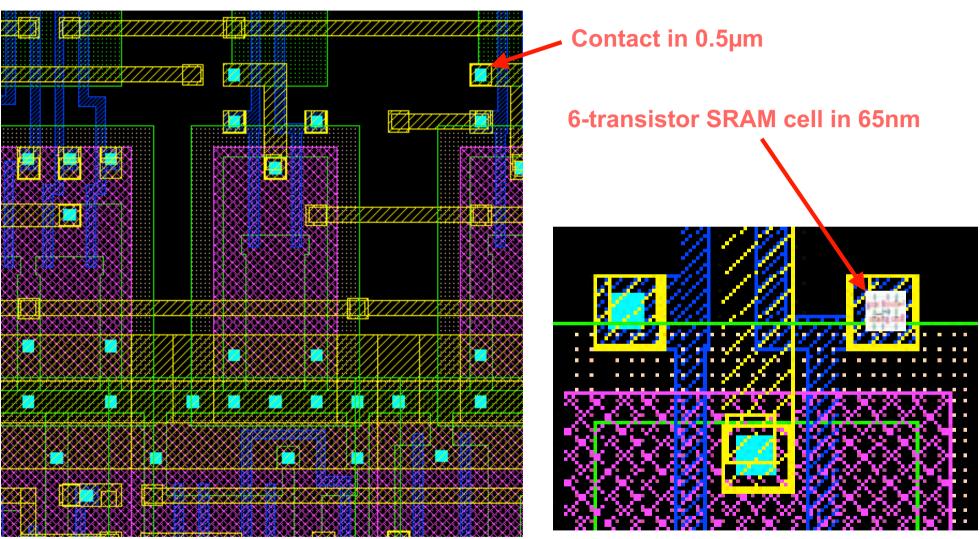

### 0.5um vs 65nm Design Rules

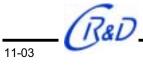

#### **CMOS Roadmap: from R&D to production**

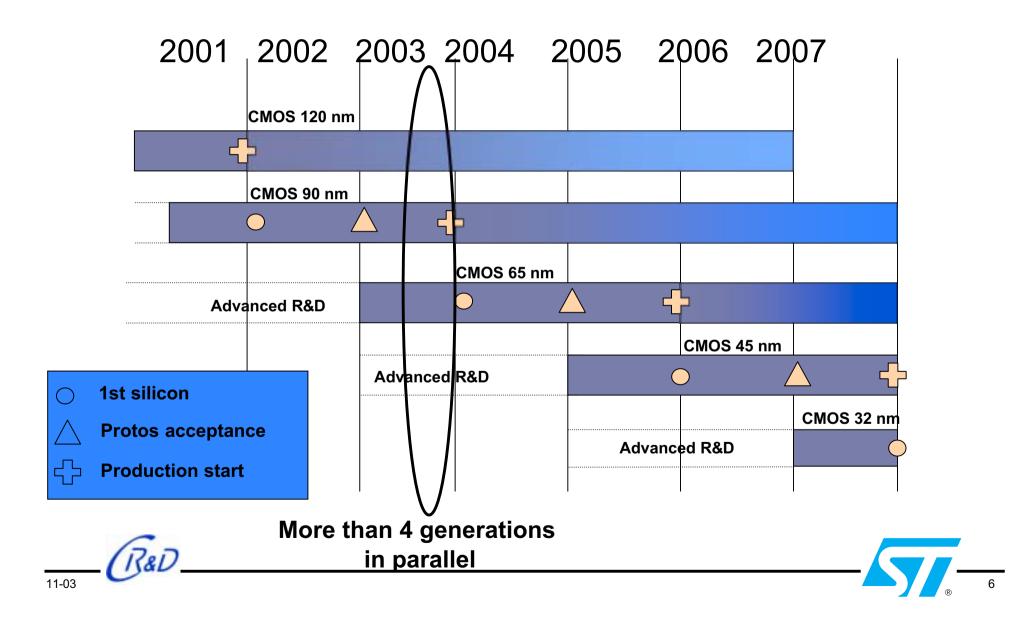

#### 45nm gate for GP device without Offset spacers

Courtesy of F. Arnaud

RED

#### **2** opposite requirements for the future

Increase processing power (GOPS):

- Video, Audio, Graphics, Communications:

- High performance dedicated processors

- A lot of embedded memories

- Replace Analog by Digital (e.g. digital Radio)

- Reduce power consumption (Watt/Op):

- Dynamic power = CV<sup>2</sup>f

- C: Need SOI-like junctions and LowK dielectrics

- V: decrease VDD to the minimum to achieve Frequency f

- F: keep Frequency pretty low, use parallelism

- Static power = as low as possible

### **Static versus Dynamic Power**

- Dynamic Power per Chip is rather stable due to system limitation: mechanical / battery

- Dynamic Power is under control:

- VDD is decreasing (slowly)

- Power management is in practice (clock gating, power shut down, ...)

- Static Power is not under control: natural leakage of transistor multiplied by 10 every 2 years:

- Power shut down is the best way to cut leakage

- Very low voltage retention or zero leakage Non Volatile memories are potential solutions

- Static Power is becoming as big as Dynamic Power at high temperature (wasted power, no solution)

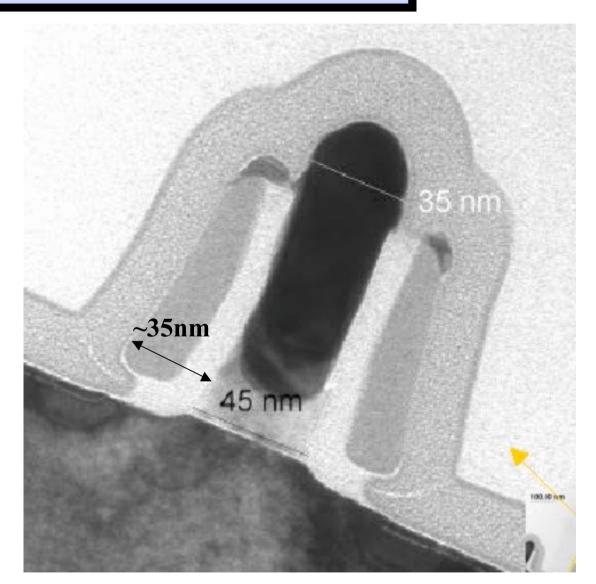

### **Nmos Ion/Ioff evolution**

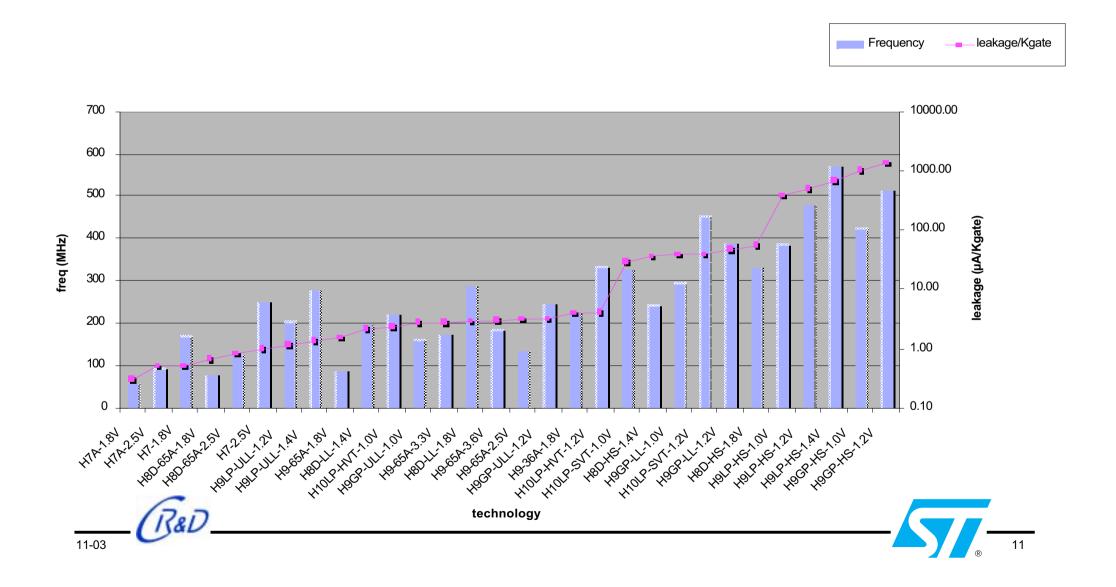

### SoC Frequency & Leakage evolution from 250nm to 90nm

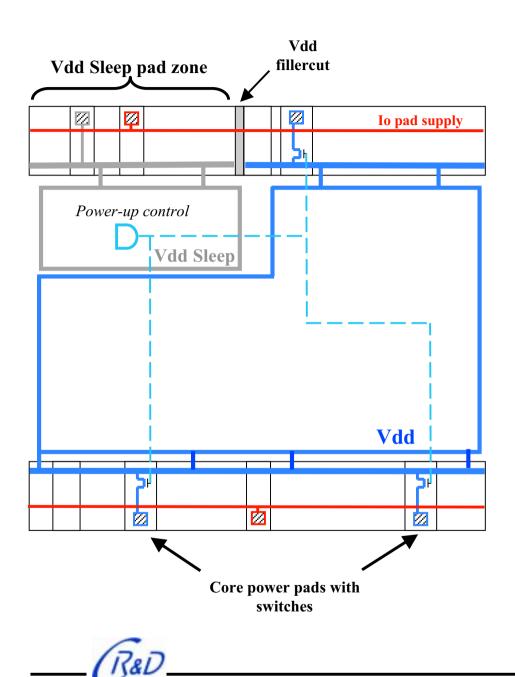

#### Low-Power techniques for wireless

- Two supply zones: Vdd and VddSleep.

- Specific rules at RTL for boundary between Vdd and VddSleep areas

- Gnd is common for all cells.

- Pads are always powered.

- 3 power pads with embedded switches

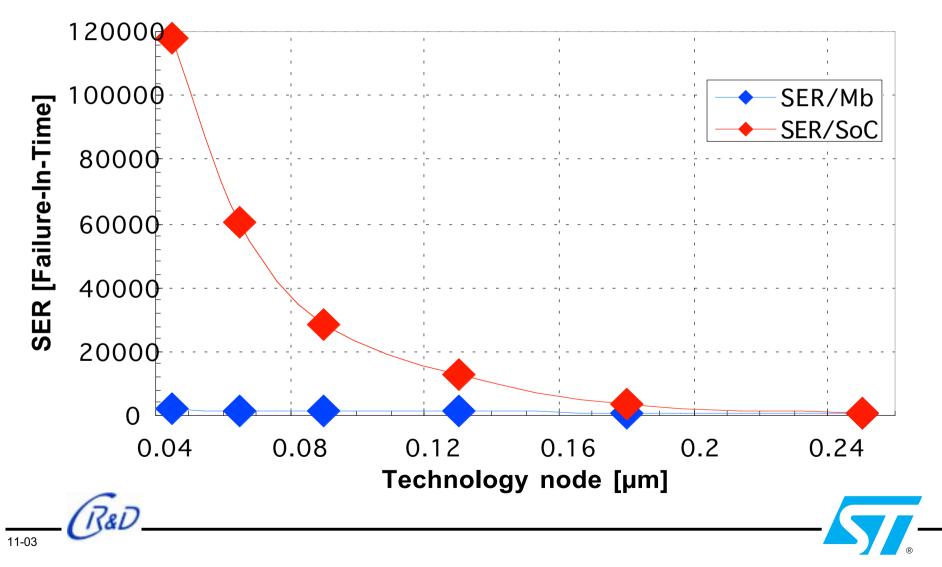

#### SoC SER increase with technology down scaling

The percentage of SRAM per System on Chip (SoC ) is derived from ITRS 2002

#### Same trend for total Standby Power !

### Agenda

Technology Evolution

- New system requirements

- Hardware/Software co-design

- Design Complexity and manufacturing costs

- Concurrent hard/software design and validation

- Flexible and Reconfigurable SoC

Conclusion

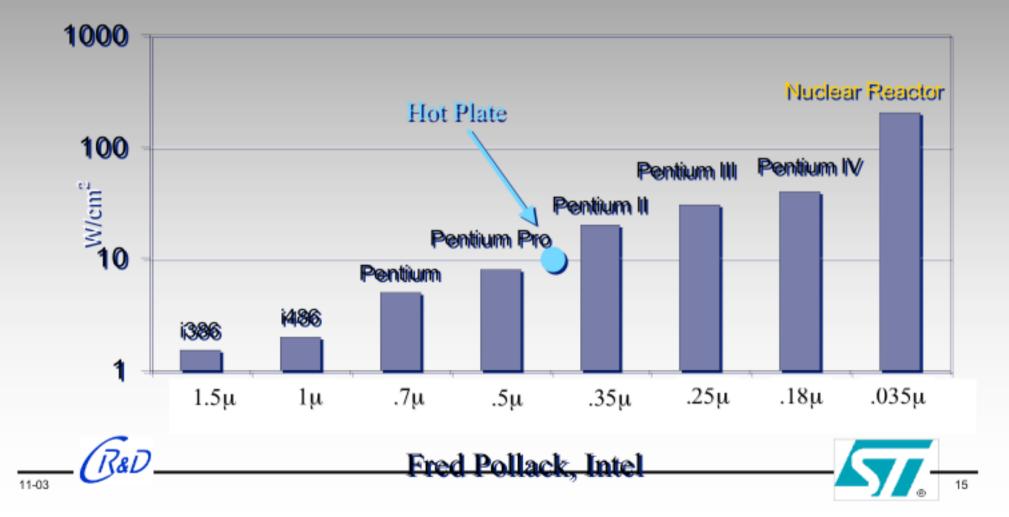

#### Power Density in Microprocessors

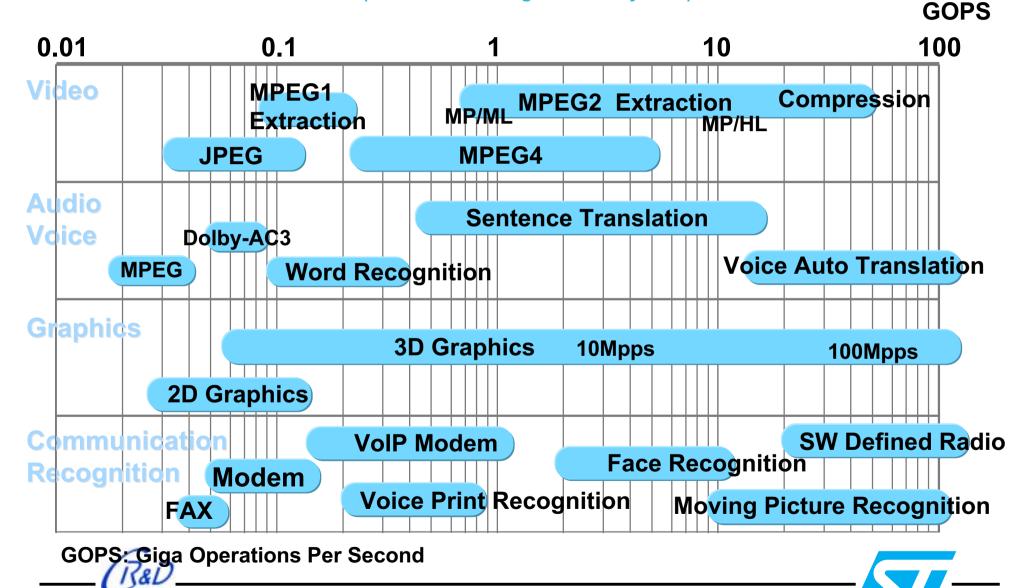

#### **Required Performance for Multi-Media Processing**

(source ITRS Design ITWG July 2003)

D

#### **PDA Model Characteristics** (source ITRS Design ITWG July 2003)

| Process Technology (nm)                         | 130             | 90                                                      | 65            | 45                       | 32        | 22     |

|-------------------------------------------------|-----------------|---------------------------------------------------------|---------------|--------------------------|-----------|--------|

| <b>Operation Voltage (V)</b>                    | 1.2             | 1                                                       | 0.8           | 0.6                      | 0.5       | 0.4    |

| Clock Frequency (MHz)                           | 150             | 300                                                     | 450           | 600                      | 900       | 1200   |

| Application                                     | Still Image     | Real Time Vid                                           | eo Codec      | Real Time Interpretation |           |        |

| (MAX performance required)                      | Processing      | (MPEG4/CIF)                                             |               |                          |           |        |

| Application                                     | Web Browser     | TV Telephone                                            | (1:1)         | TV Telephor              | ne (>3:1) |        |

| (Others)                                        | Electric Mailer | Voice Recognition (Input) Voice Recognition (Operation) |               |                          | ion)      |        |

|                                                 | Scheduler       | Authentication                                          | (Crypto Engin | ne)                      |           |        |

| Processing Performance (GOPS)                   | 0.3             | 2                                                       | 14            | 77                       | 461       | 2458   |

| Parallelism Factor                              | 1               | 4                                                       | 4             | 4                        | 4         | 4      |

| Communication Speed (Kbps)                      | 64              | 384                                                     | 2304          | 13824                    | 82944     | 497664 |

| Power Consumption (MOPS/mW)                     | 3               | 20                                                      | 140           | 770                      | 4160      | 24580  |

| Peak Power Consumption (mW)<br>(Requirement)    | 100             | 100                                                     | 100           | 100                      | 100       | 100    |

| Standby power consumption (mW)<br>(Requirement) | 2               | 2                                                       | 2             | 2                        | 2         | 2      |

| Battery Wh/Kg                                   | 120             | 200 400                                                 |               |                          |           |        |

|                                                 |                 |                                                         |               |                          |           |        |

RED 11-03

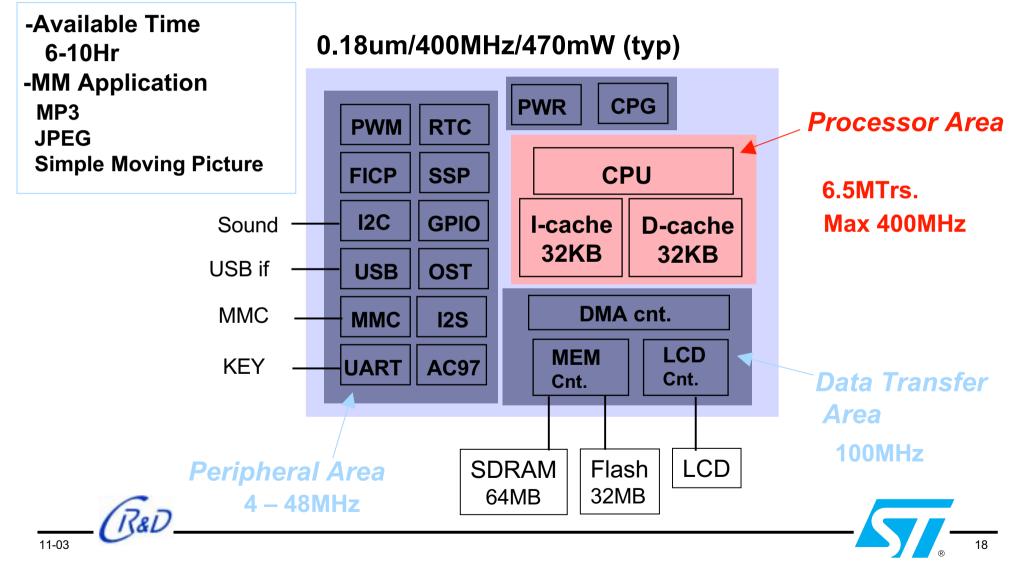

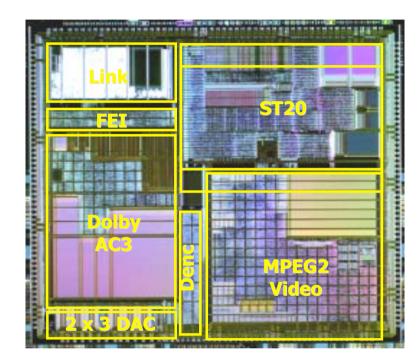

#### An Example of SoC for PDA

(source ITRS Design ITWG July 2003)

#### **Specification**

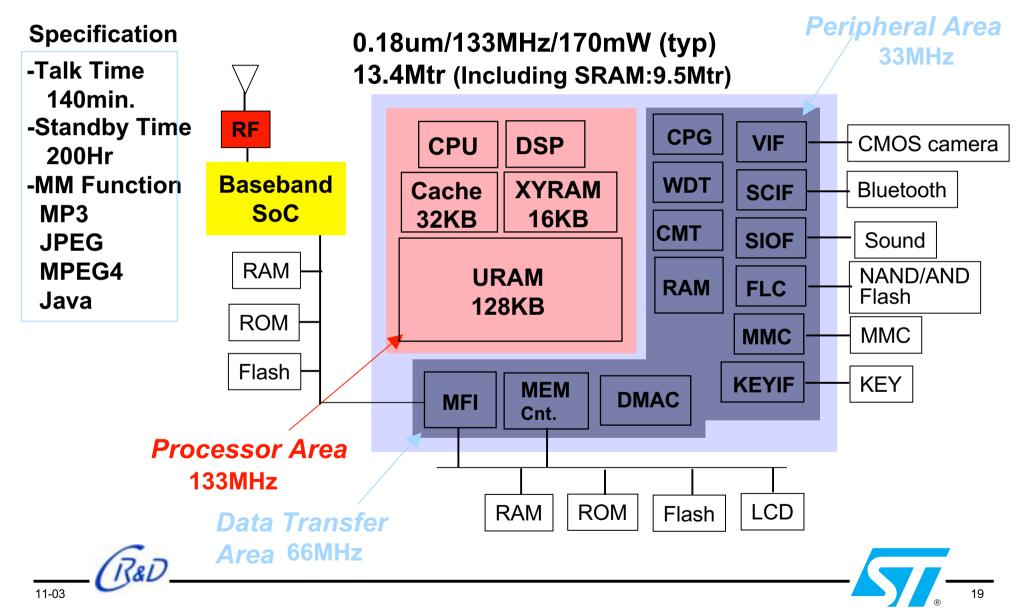

#### An Example of SoC for Mobile Phone

(source ITRS Design ITWG July 2003)

### SoC at the heart of conflicting trends

Time-to-market: **Process roadmap** acceleration Consumerization of electronic devices

**Complex systems:** uCs, DSPs HW/SW SW protocol stacks **RTOS.s Digital/Analog IPs On-Chip busses Process options** explosion (analog, RF, imagers, ...)

Deep sub micron effects:

crosstalk electro migration wire delays, on-chip-variation mask costs (OPC, PSM) copper wires

### Agenda

- Technology Evolution

- New system requirements

- Hardware/Software co-design

- Design Complexity and manufacturing costs

- Concurrent hard/software design and validation

- Flexible and Reconfigurable SoC

- Conclusion

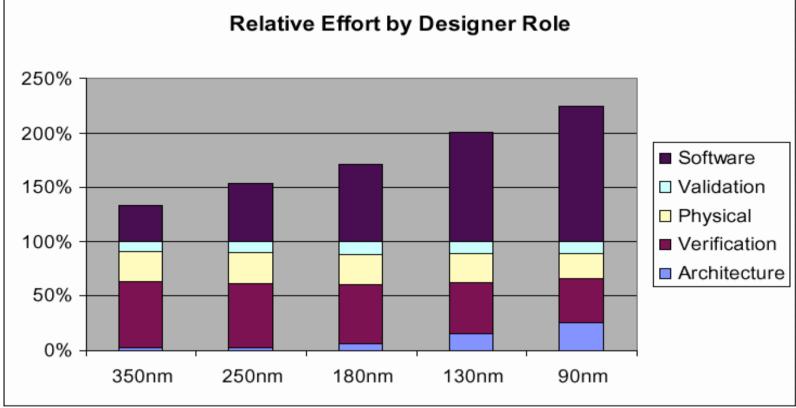

### SoC Design + Rising Complexity = New Challenges

**IBS Nov 2002**

- \* Architecture effort overtakes physical design at 90nm

- \* Software costs overtake total hardware costs at 130nm

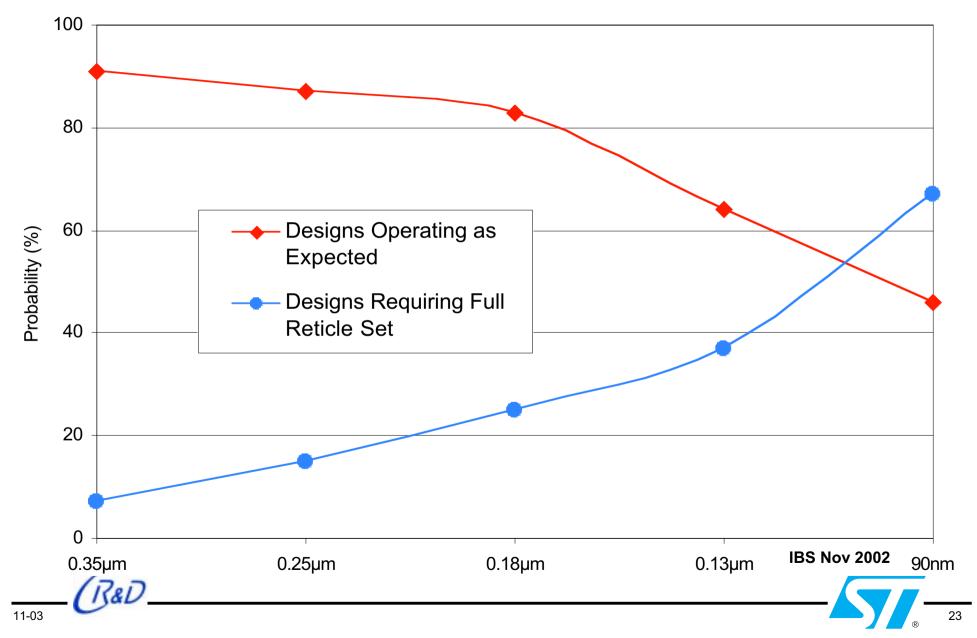

#### **PROBABILITY OF DESIGNS OPERATING AS EXPECTED**

### Key Trends: ASICs down, Multi-processors & FPGAs up

- ASIC/ASSP ratio: 80/20 in 2000, 50/50 in 2003

- Telecom company trends

- In-house ASIC design way down

- Replace by commercial off-the-shelf, programmable ASSP

- High-end NPU's used in non-NPU applications

- Number of embedded processors in SoC rising:

| — | ST: recordable DVD     | 5    |

|---|------------------------|------|

| — | Hughes: set-top box    | 7    |

| — | ST: HDTV platform      | 8    |

| — | Latest mobile handsets | 10   |

| — | NEC: Image processor   | 128  |

| _ | In-house NPU           | >150 |

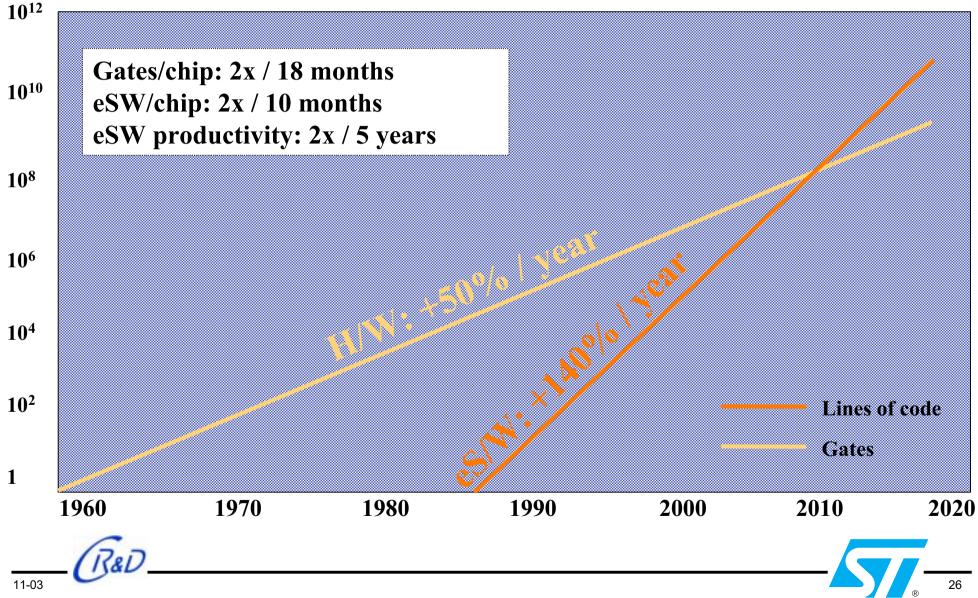

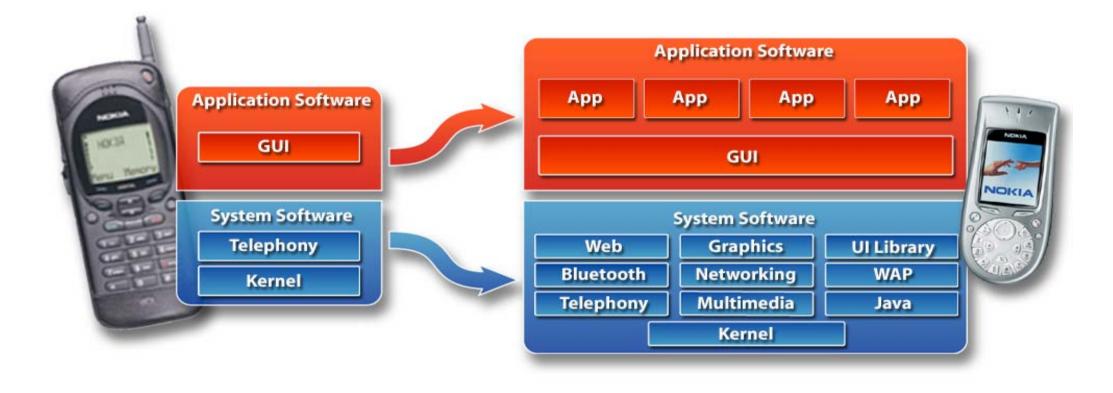

### Key Trends: Embedded S/W content in SoC is way up

- eS/W: Current application complexity

- Set-top box: >1 million lines of code

- Digital audio processing: >1 million lines of code

- Recordable DVD: Over 100 person-years effort

- Hard-disk drive: eS/W represents 100 person-years effort

- In multimedia systems

- S/W cost (licenses, royalties) 6X larger than H/W chip cost

- eS/W uses 50% to 80% of design resources

- eS/W has become an essential part of SoC products

- Software reuse essential now

- Software architecture becoming important

- Memory now dominating die area

### S/W and H/W Complexity Factors

### Agenda

- Technology Evolution

- New system requirements

- Hardware/Software co-design

- Design Complexity and manufacturing costs

- Concurrent hard/software design and validation

- Flexible and Reconfigurable SoC

- Conclusion

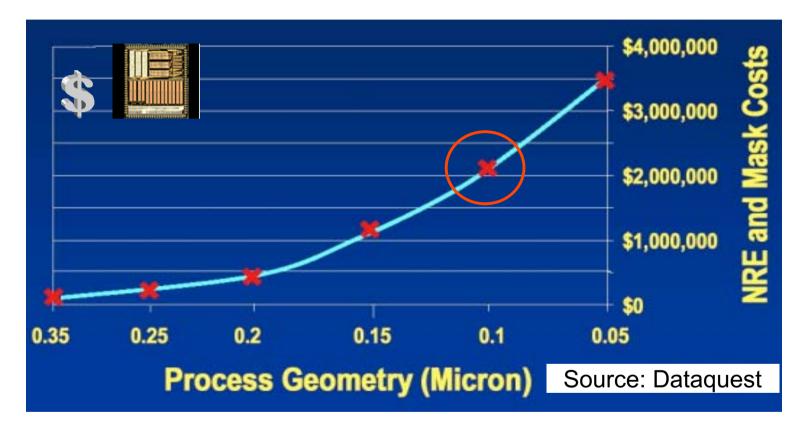

### SoC Economic Trends: Mask NRE

For \$5 ASP with 25% profit margin: Need to sell over 1.6M parts to break even

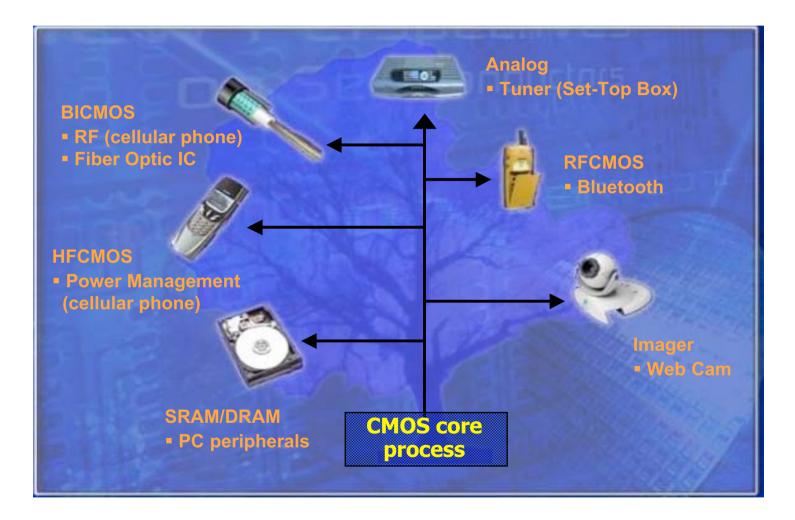

### **Extending Core CMOS for SOC**

RED

### Deep Submicrons Effects modeled in 0.13um

Voltage Drop & EMG

Copper Routing

Cross Talk effects

Substrate Noise

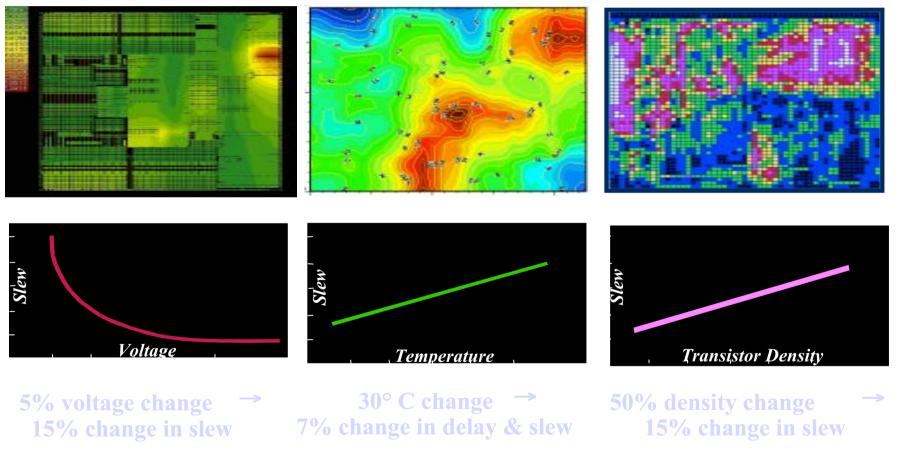

### **New Timing Effects (90nm)**

Voltage on-chip-variations Temperature Map

**Transistor Density**

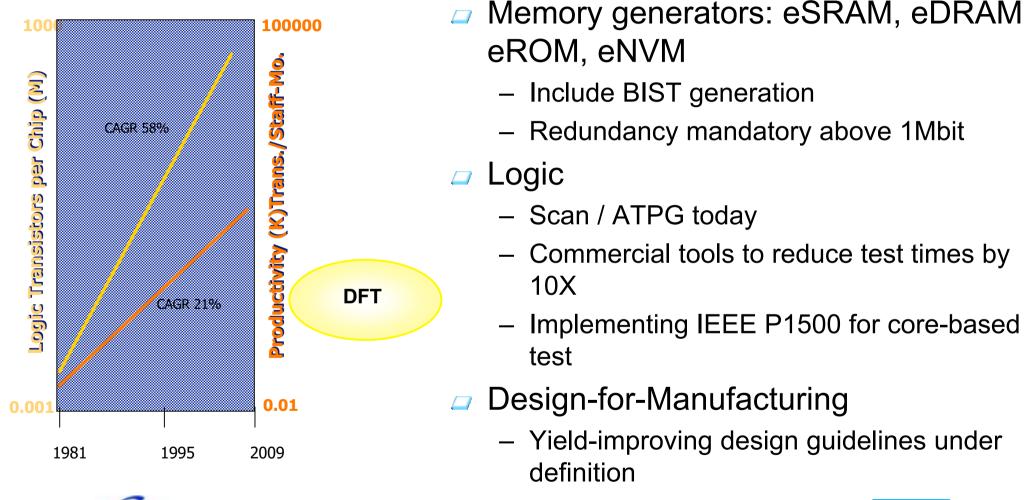

### **Design For Test**

11-03

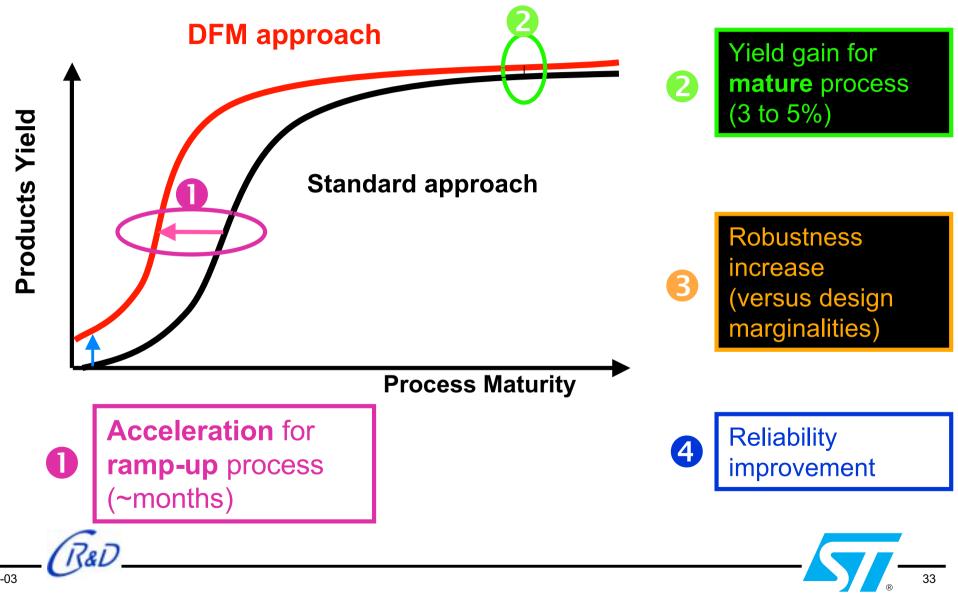

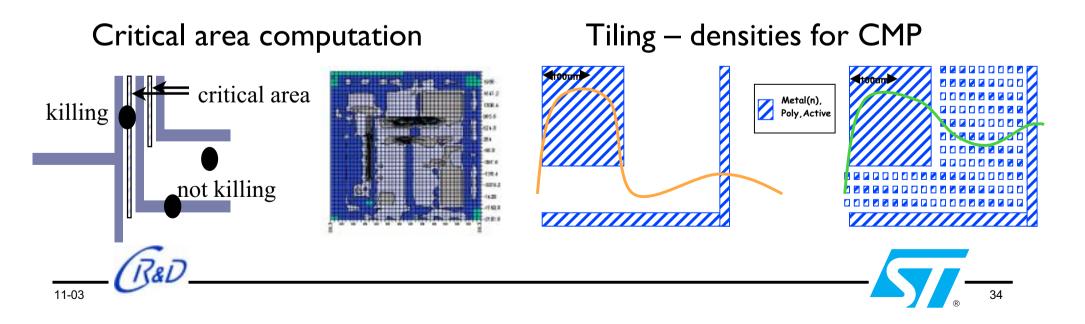

### **Design For Manufacturability Gains**

## **Design For Manufacturability**

#### Misalignment impact

#### Matching robustness

#### Wire spreading

### **SoC**,s with **CMOS**-Imager process

#### **Given Series and Seri**

✓ **ZS450**: CIF format (~100000 pixels)

Area 24.0 mm

✓ **ZS550**: VGA format (~300000 pixels)

Area **39.6 mm**

#### **Given Series and Seri**

✓ **ZS422**: QVGA format (~75000 pixels)

Area

=> audio/video processing (SOC)

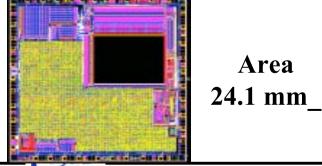

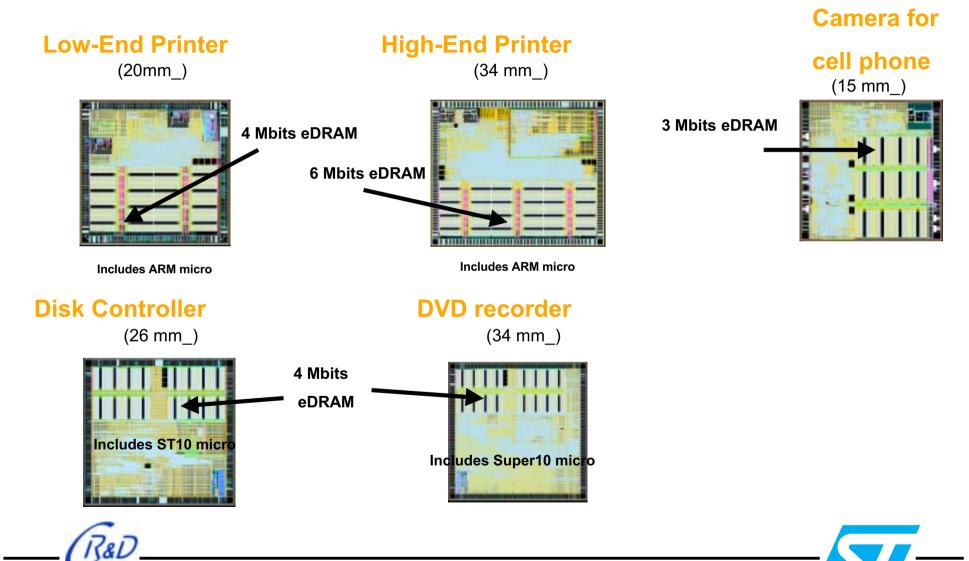

# Production 0.18um SoC,s with eDRAM

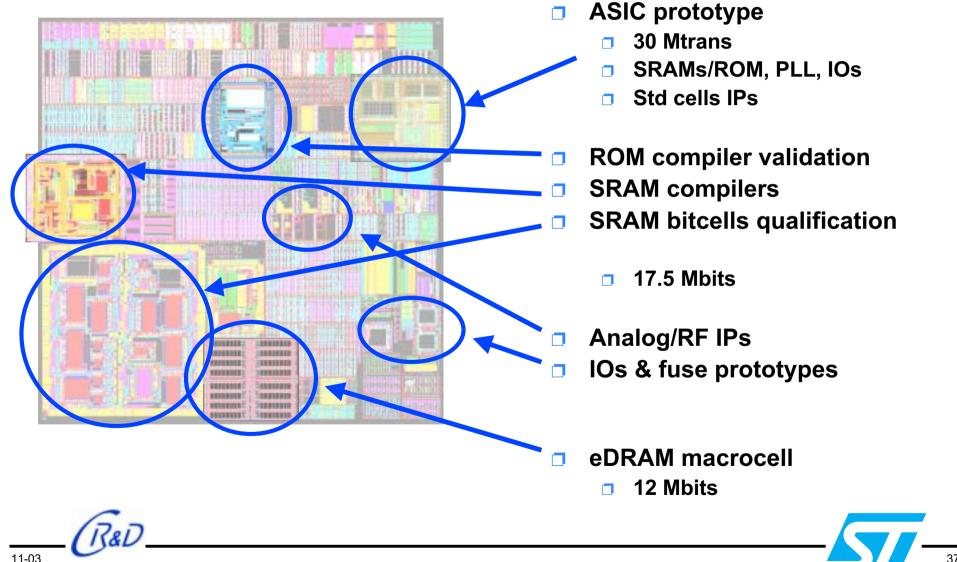

#### **IP & design validation effort** case study – 90nm test masks

### **Emb.memory offering expanding**

| _        |                       | 0.13um     | 90nm       |

|----------|-----------------------|------------|------------|

| ſ        |                       | spsmall    | spsmall    |

| ST       | <b>Register files</b> |            | dpreg      |

| Partners |                       | dprf       | dprf       |

|          | High density          | sphd       | sphd       |

|          |                       | dphd       | dphd       |

|          |                       | spuhd      | spuhd      |

|          | High speed            | sphs       | sphs       |

|          |                       |            | spuhs      |

|          |                       | dphs       | dphs       |

|          | High capacity         | splarge    | splarge    |

|          | Low Power             | starsplp   | starsplp   |

|          |                       |            | splp       |

|          |                       |            | dplp       |

|          | rom                   | romv       | romv       |

|          |                       | romclp     |            |

| -        | Multi port            | тра        | multiport  |

|          | САМ                   | bcam, tcam | bcam, tcam |

|          | Cache (data and tag)  |            | spcache    |

## Agenda

- Technology Evolution

- New system requirements

- Hardware/Software co-design

- Design Complexity and manufacturing costs

- Concurrent hard/software design and validation

- Flexible and Reconfigurable SoC

- Conclusion

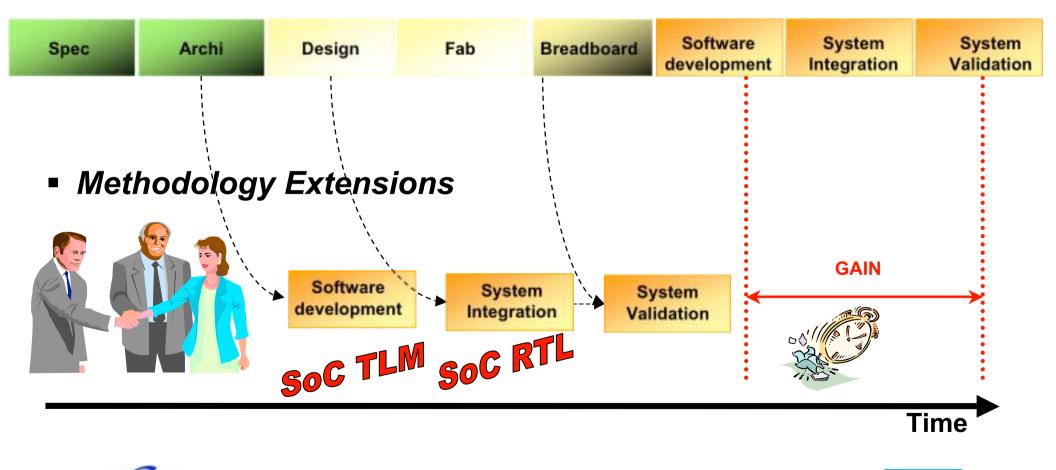

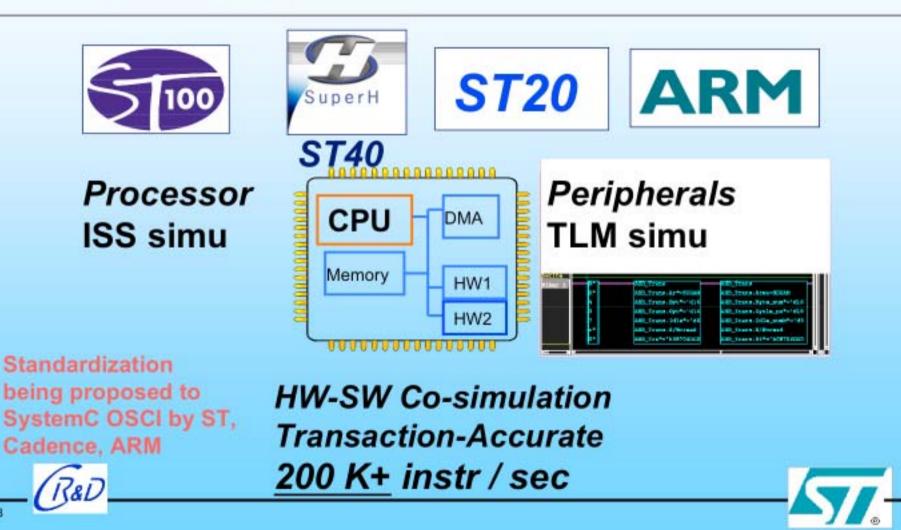

#### **Concurrent Hardware/Software Design**

Standard Flow

(R&D

#### Embedded Software Development Requires as Much/More Design Effort Than Hardware

RED

#### **Operating-System is booting on simulated Cellphone (RTL)**

Software Real RTOS (Symbian)

Processor

**ISS** simu

DMA

HW1

HW2

CPU

Memory

HW-SW Co-simulation

Cycle-Accurate

200 instr / sec

#### *Peripherals* RTL simulation

RaD

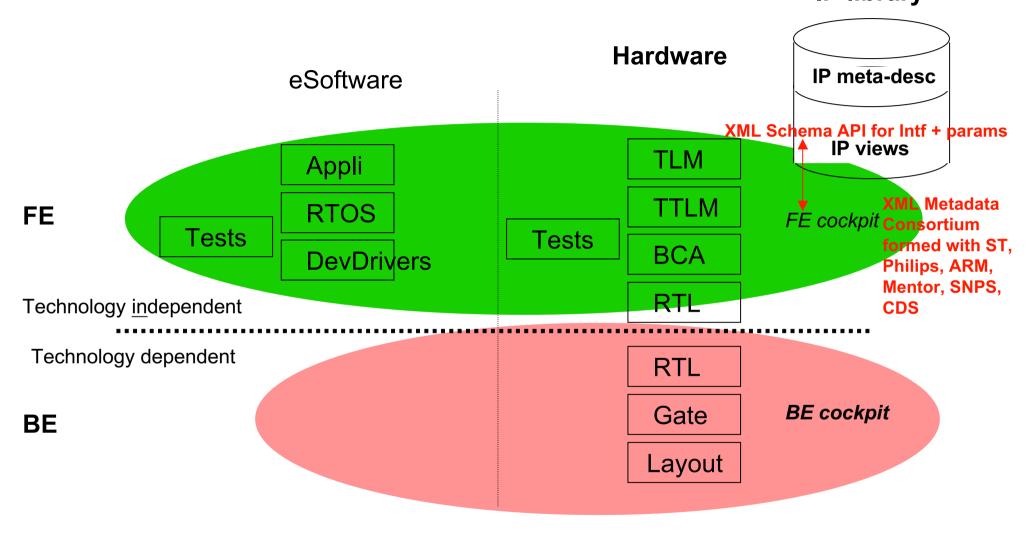

## **TLM models - Fast SoC simulations**

## Real embedded Software

**Application & Functional Verification**

## **Platform-based design flow**<sub>IP library</sub>

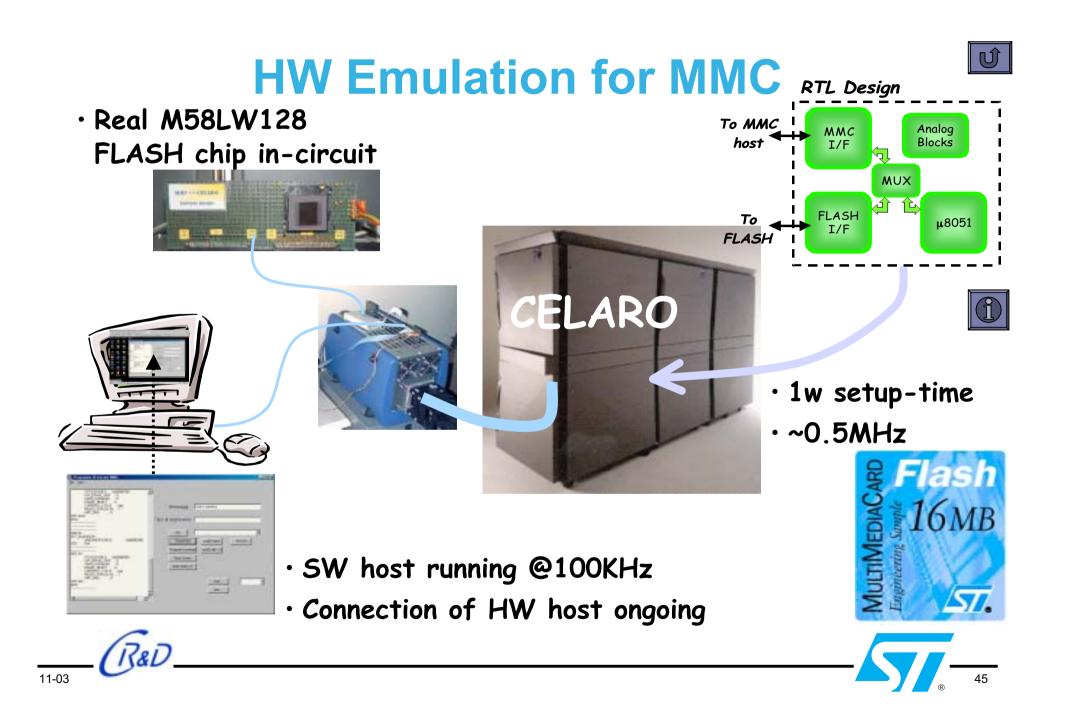

#### **First Prototype Platform: Aptix**

11-03

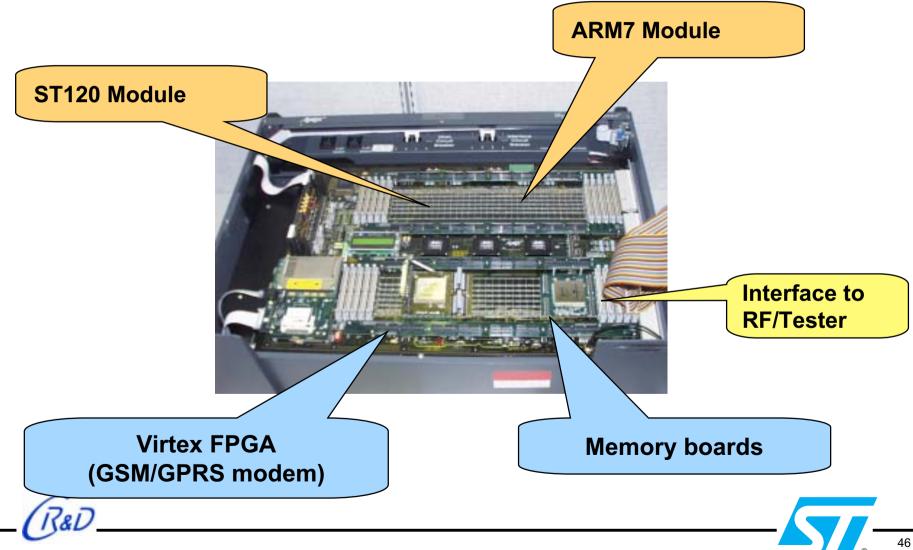

## HW/SW fast prototype platform

- Faithful representation of the final design

- Available much sooner than the final silicon

- Guaranties the real-time behavior

- Validation of the fundamentals of the SoC HW/SW architecture

#### **FPGA-based Prototyping Environment**

#### **IP Reuse Program**

CAD On Line portal > K9 IP Reuse Pages

CR&D + cross-divisional Committee

VSIA: RMM: Quality

"Design Methodology & IP Reuse", CEO sponsored

RTL2Layout, AMS, SLD, DFT, Functional Verif., Power, ...

- company program

- corporate driven

- domain-specific Work Groups

- intranet information site

#### Reuse standards

- adherence to industry approach

- deliverables / views

- IP packaging

- HDL coding style

- On Chip Bus

# The Blue Book

577

#### □ Methodology

- Development flow

- OCB support

- System Level

- Verification

#### □ Infrastructure

- Design Data Manag<sup>t</sup>., Bug tracking

- IP Quality (IP=Product)

- IP Procurement

Products from Synchronicity, Rational IPScreen Certification; LibYield Maturity tracking IP On Line catalog; Procurement, Exchange procedures

BlueBook + Unicad Extension bbview (mapping from BB logic views to IP physical files) Design Conventions + HAL associated checking tool VCI-close STBus; AMBA

Synopsys based Quartet STBus, AMBA Platform kits SL model deliverables (TLM, BCA...) dynamic, formal, H/W-S/W, integration

49

#### **Corporate IP Catalog Project**

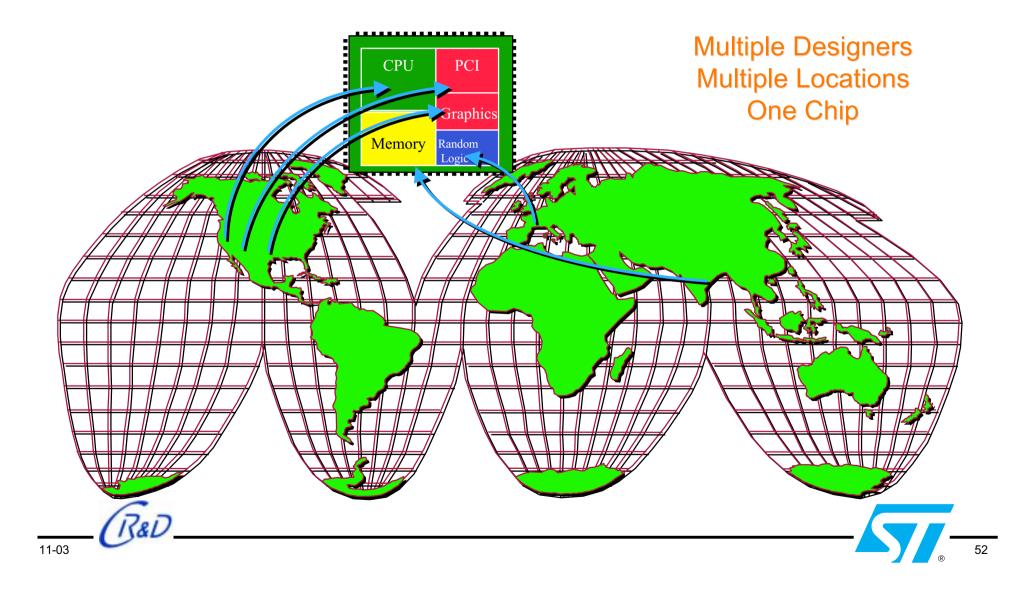

# Multi-Site Collaborative Design (Synchronicity-based)